#### **DATA SHEET**

# **SKY72310-362LF: Spur-Free, 2.1 GHz Single Fractional-N Frequency Synthesizer**

#### **Applications**

- · General purpose RF systems

- 2.5G and 3G wireless infrastructure

- · Broadband wireless access

- · Low bit rate wireless telemetry

- Instrumentation

- · L-band receivers

- Satellite communications

#### **Features**

- · Spur-free operation

- 2.1 GHz maximum operating frequency

- Ultra-fine step size, 100 Hz or less

- High internal reference frequency enables large loop bandwidth implementations

- Very fast switching speed (e.g., below 100 μs)

- Phase noise to -91 dBc/Hz inside the loop filter bandwidth

@ 1800 MHz

- Software programmable power-down modes

- High-speed serial interface up to 100 Mbps

- Three-wire programming

- · Programmable division ratios on reference frequency

- Phase detector with programmable gain to provide a programmable loop bandwidth

- Frequency power steering enhances rapid acquisition time

- On-chip crystal oscillator

- Frequency adjust for temperature compensation

- 3 V operation

- 5 V output to loop filter

- QFN (24-pin, 4 x 4 mm) Pb-free (MSL3, 260 °C per JEDEC J-STD-020) package

Skyworks Green<sup>TM</sup> products are compliant with all applicable legislation and are halogen-free. For additional information, refer to *Skyworks Definition of Green*<sup>TM</sup>, document number SQ04-0074.

# **Description**

The Skyworks SKY72310-362LF fractional-N frequency synthesizer provides ultra-fine frequency resolution, fast switching speed, and low phase-noise performance. This synthesizer is a key building block for high-performance radio system designs that require low power and fine step size.

The utra-fine step size of less than 100 Hz allows this synthesizer to be used in very narrowband wireless applications. With proper temperature sensing or through control channels, the synthesizer's fine step size can compensate for crystal oscillator or intermediate frequency (IF) filter drift. As a result, crystal oscillators or crystals can replace temperature-compensated or ovenized crystal oscillators, reducing parts count and associated component cost. The device's fine step size can also be used for Doppler shift corrections.

The SKY72310-362LF has a phase noise floor of -90 dBc/Hz up to 2.1 GHz operation as measured inside the loop bandwidth. This is permitted by the on-chip low noise dividers and low divide ratios provided by the device's high fractionality.

Reference crystals or oscillators up to 50 MHz can be used with the SKY72310-362LF. The crystal frequency is divided down by independent programmable dividers (1 to 32) for the synthesizer. The phase detector can operate at a maximum speed of 25 MHz, which allows better phase noise due to the lower division value. With a high reference frequency, the loop bandwidths can also be increased. Larger loop bandwidths improve the settling times and reduce in-band phase noise. Therefore, typical switching times of less than 100  $\mu s$  can be achieved. The lower in-band phase noise also permits the use of lower cost voltage controlled oscillators (VCOs) in customer applications.

The SKY72310-362LF has a frequency power steering circuit that helps the loop filter to steer the VCO when the frequency is too fast or too slow, further enhancing acquisition time.

The unit operates with a three-wire, high-speed serial interface. A combination of large bandwidth, fine resolution, and the three wire interface allows for direct frequency modulation of the VCO. This supports any continuous phase, constant envelope modulation scheme such as frequency modulation (FM), frequency shift keying (FSK), minimum shift keying (MSK), or Gaussian minimum shift keying (GMSK).

This capability can eliminate the need for in-phase and quadrature (I/Q) digital-to-analog converters (DACs), quadrature upconverters, and IF filters from the transmitter portion of the radio system.

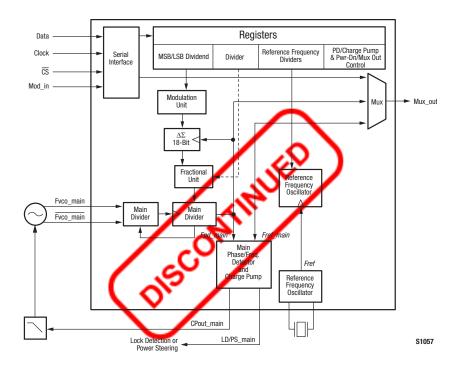

Figure 1 shows a functional block diagram for the SKY72310-362LF. The device package and pinout for the 24-pin Quad Flat No-Lead (QFN) package are shown in Figure 2.

Figure 1. SKY72310-362LF Functional Block Diagram

Figure 2. SKY72310-362LF Pinout (Top View)

#### **Technical Description**

The SKY72310-362LF is a fractional-N frequency synthesizer using a  $\Delta\Sigma$  modulation technique. The fractional-N implementation provides low in-band noise by having a low division ratio and fast frequency settling time. In addition, the SKY72310-362LF provides arbitrarily fine frequency resolution with a digital word, so that the frequency synthesizer can be used to compensate for crystal frequency drift in the RF transceiver.

#### **Serial Interface**

The serial interface is a versatile three-wire interface consisting of three pin signals: Clock (serial clock), Data (serial input), and  $\overline{\text{CS}}$  (chip select). It enables the SKY72310-362LF to operate in a system where one or multiple masters and slaves are present. To perform a loopback test at startup and to check the integrity of the board and processor, the serial data is fed back to the master device (e.g., a microcontroller or microprocessor unit) through a programmable multiplexer. This facilitates hardware and software debugging.

#### $\Delta\Sigma$ Modulator

The SKY72310-362LF provides fractionality through the use of proprietary, configurable 10-bit or 18-bit  $\Delta\Sigma$  modulator. The output from the modulator is combined with the divider ratio through its fractional units.

#### **VCO Prescaler**

The VCO prescaler provides low-noise signal conditioning of the VCO signal. It translates an off-chip, single-ended or differential signal to an on-chip differential Current Mode Logic (CML) signal.

#### **VCO Divider**

The SKY72310-362LF provides a programmable divider that controls the CML prescaler and supplies the required signal to the charge pump phase detector. Programmable divide ratios ranging from 38 to 537 are possible in fractional-N mode and from 32 to 543 in integer-N mode.

#### **Reference Frequency Oscillator**

The SKY72310-362LF has a self-contained, low-noise crystal oscillator. This crystal oscillator is followed by the clock generation circuitry that generates the required clock for the programmable reference frequency divider.

#### **Reference Frequency Divider**

The crystal oscillator signal can be divided by a ratio of 1 to 32 to create the reference frequency for the phase detector. The divide ratio is programmed using the Reference Frequency Dividers Register.

**NOTE**: The divided crystal oscillator frequency (the internal reference frequency), Fref\_main, is referred to as "reference frequency" throughout this document.

#### **Phase Detector and Charge Pump**

The SKY72310-362LF uses a charge pump phase detector that provides a programmable gain, Kd, from 31.25 to 1000  $\mu$ A/2 $\pi$  radians in 32 steps. The phase detector is programmed using the Phase Detector/Charge Pump Control Register.

#### **Frequency Steering**

When programmed for frequency power steering, the SKY72310-362LF has a circuit that helps the loop filter steer the VCO using the LD/PSmain signal (pin 4). In this configuration, the LD/PSmain signal can provide a more rapid acquisition.

When programmed for lock detection, internal frequency steering is implemented and provides frequency acquisition times comparable to conventional phase/frequency detectors.

#### **Lock Detection**

When programmed for lock detection, the SKY72310-362LF provides an active low, pulsing open collector output using the LD/PSmain signal (pin 4) to indicate the out-of-lock condition. When locked, the LD/PSmain signal is tri-stated (high impedance).

#### **Power Down**

The SKY72310-362LF supports a number of power-down modes through the serial interface. For more information, see the Register Descriptions section of this document.

# **Serial Interface Operation**

The serial interface consists of three pins: Clock (pin 22), Data (pin 20), and  $\overline{\text{CS}}$  (pin 21). The Clock signal controls data on the two serial data lines (Data and  $\overline{\text{CS}}$ ). The Data pin shifts bits into a temporary register on the rising edge of Clock. The  $\overline{\text{CS}}$  signal allows individual selection transfers that synchronize and sample the information of slave devices on the same bus.

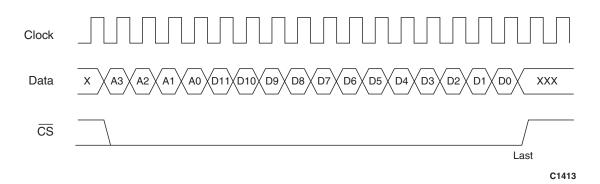

Figure 3 functionally depicts how a serial transfer takes place. A serial transfer is initiated when a microcontroller or microprocessor forces the  $\overline{\text{CS}}$  signal to a low state. This is followed immediately by an address/data stream sent to the Data pin that coincides with the rising edges of the clock presented at the Clock pin.

Each rising edge of the Clock signal shifts in one bit of data on the Data line into a shift register. At the same time, one bit of data is shifted out of the Mux\_out pin (if the serial bit stream is selected) at each falling edge of Clock. To load any of the registers, 16 bits

of address or data must be presented to the Data line with the LSB last while the  $\overline{CS}$  signal is low. If the  $\overline{CS}$  signal is low for more than 16 clock cycles, only the last address or data bits are used to load the registers.

#### **Register Programming**

Register programming equations, described in this section, use the following variables and constants:

N<sub>fractional</sub> Desired VCO division ratio in fractional-N applications. This is a real number and can be interpreted as the

> reference frequency  $(F_{ref})$  multiplying factor so that the resulting frequency is equal to the desired VCO

frequency.

Ninteger Desired VCO division ratio in integer-N applications.

This number is an integer and can be interpreted as the reference frequency  $(F_{ret})$  multiplying factor so that the resulting frequency is equal to the desired VCO

frequency.

Nine-bit unsigned input value to the divider ranging  $N_{reg}$ from 0 to 511 (integer-N mode) and from 6 to 50

(fractional-N mode).

divider This constant equals 262144 when the  $\Delta \Sigma$  modulator

is in 18-bit mode, and 1024 when the  $\Delta\Sigma$  modulator is

in 10-bit mode.

Fdiv ref/210 Hz.

dividend When in 18-bit mode, this is the 18-bit signed input value to the  $\Delta\Sigma$  modulator, ranging from -131072 to

+131071 and providing 262144 steps, each step equal to  $F_{div}$  ref  $2^{18}$  Hz.

When in 10-bit mode, this is the 10-bit signed input value to the  $\Delta\Sigma$  modulator, ranging from -512 to +511 and providing 1024 steps, each step equal to

$F_{VCO}$ Desired VCO frequency.

F<sub>div ref</sub> Divided reference frequency presented to the phase

detector.

Fractional-N Applications. The desired division ratio for the synthesizer is given by:

$$N_{fractional} = \frac{F_{VCO}}{F_{div} ref}$$

where  $N_{fractional}$  must be between 37.5 and 537.5.

The value to be programmed in the Divider Register is given by:

$$N_{reg} = Round(N_{fractional}) - 32$$

**NOTE**: The Round function rounds the number to the nearest

When in fractional mode, allowed values for  $N_{reg}$  are from 6 to 505 inclusive.

The value to be programmed by either of the Dividend Registers (MSB or LSB) is given by:

$$dividend = Round[divider \times (N_{fractional} - N_{reg} - 32)]$$

where the divider is either 1024 in 10-bit mode or 262144 in 18-bit mode. Therefore, the dividend is a signed binary value either 10 or 18 bits long.

**NOTE**: Because of the high fractionality of the SKY72310-362LF. there is no practical need for any integer relationship between the reference frequency and the channel spacing or desired VCO frequencies.

Sample calculations for two fractional-N applications are provided in Figure 4.

**Figure 3. Serial Transfer Timing Diagram**

Case 1: To achieve a desired Fvco\_main frequency of 902.4530 MHz using a crystal frequency of 40 MHz with operation of the synthesizer in 18-bit mode. Since the maximum internal reference frequency (Fdiv\_ret) is 25 MHz, the crystal frequency is divided by 2 to obtain a Fdiv\_ret of 20 MHz. Therefore:

$$\begin{array}{rcl}

N fractional & = & Fvco\_main \\

\hline

F div\_ref \\

& = & \frac{902.4530}{20} \\

& = & 45.12265

\end{array}$$

The value to be programmed in the Divider Register is:

With the modulator in 18-bit mode, the value to be programmed in the Dividend Registers is:

dividend = Round[divider

$$\times$$

(Niractional - Nireg - 32)]

= Round[262144  $\times$  (45.12265 - 13 - 32)]

= Round[262144  $\times$  (0.12265)]

= Round[32151.9616]

= 32152 (decimal)

= 000111110110011000 (binary)

where 00 0111 1101 is loaded in the Dividend MSB Register and 1001 1000 is loaded in the Dividend LSB Register.

#### Summary:

- Divider Register = 0 0000 1101

- Dividend LSB Register = 1001 1000

- Dividend MSB Register = 00 0111 1101

- · The resulting VCO frequency is 902.453 MHz

- Step size is 76.3 Hz

Note: The frequency step size for this case is 20 MHz divided by 2<sup>18</sup>, giving 76.3 Hz.

S1059

Figure 4. Fractional-N Applications: Sample Calculation (1 of 2)

Case 2: To achieve a desired Fvco\_main frequency of 917.7786 MHz using a crystal frequency of 19.2 MHz with operation of the synthesizer in 10-bit mode. Since the maximum internal reference frequency (Fdiv\_ret) is 25 MHz, the crystal frequency does not require the internal division to be greater than 1, which makes Fdiv\_ret = 19.2 MHz. Therefore:

The value to be programmed in the Divider Register is:

With the modulator in 10-bit mode, the value to be programmed in the Dividend Registers is:

where 11 0011 0100 is loaded in the Dividend MSB Register.

#### Summary:

- Divider Register = 0 0001 0000

- Dividend MSB Register = 11 0011 0100

- The resulting VCO frequency is 917.775 MHz

- Step size is 18.75 kHz

Note: The frequency step size for this case is 19.2 MHz divided by 2<sup>10</sup>, giving 18.75 kHz.

S1060

Figure 4. Fractional-N Applications: Sample Calculation (2 of 2)

**Integer-N Applications**. The desired division ratio for the synthesizer is given by:

$$N_{int \, eger} = \frac{F_{vco\_main}}{F_{div\_ref}}$$

where N<sub>integer</sub> is an integer number from 32 to 543.

The value to be programmed in the Divider Register is given by:

$$N_{reg} = N_{int\,eger} - 32$$

When in integer mode, allowed values for  $N_{reg}$  are from 0 to 511.

**NOTE**: As with all integer-N synthesizers, the minimum step size is related to the crystal frequency and reference frequency division ratio.

Register Loading Order. In applications where the synthesizer is in 18-bit mode, the Dividend MSB Register holds the 10 MSBs of the dividend and the Dividend LSB Register holds the 8 LSBs of the dividend. The registers that control the synthesizer's divide ratio are to be loaded in the following order:

- Divider Register

- Dividend LSB Register

- Dividend MSB Register (at which point the new divide ratio takes effect)

In applications where the synthesizer is in 10-bit mode, the Dividend MSB Register holds the 10 bits of the dividend. The registers that control the synthesizer's divide ratio are to be loaded in the following order:

- Divider Register

- Dividend MSB Register (at which point the new divide ratio takes effect)

**NOTE**: When in integer mode, the new divide ratios take effect as soon as the Divider Register is loaded.

#### **Direct Digital Modulation**

The high fractionality and small step size of the SKY72310-362LF allow the user to tune to practically any frequency in the VCO's operating range. This allows direct digital modulation by programming the different desired frequencies at precise instants. Typically, the channel frequency is programmed by the Main Divider and MSB/LSB Dividend Registers, and the instantaneous frequency offset from the carrier is programmed by the Modulation Data Register.

The Modulation Data Register can be accessed in three ways as defined in the following subsections.

**Normal Register Write**. A normal 16-bit serial interface write occurs when the  $\overline{\text{CS}}$  signal is 16 clock cycles wide. The corresponding 16-bit modulation data is simultaneously

presented to the Data pin. The content of the Modulation Data Register is passed to the modulation unit at the next falling edge of the divided main VCO frequency ( $F_{pd}$  main).

Short  $\overline{\text{CS}}$  Through Data Pin (No Address Bits Required). A shortened serial interface write occurs when the  $\overline{\text{CS}}$  signal is from 2 to 12 clock cycles wide. The corresponding modulation data (2 to 12 bits) is simultaneously presented to the Data pin. The Data pin is the default pin used to enter modulation data directly in the Modulation Data Register with shortened  $\overline{\text{CS}}$  strobes.

This method of data entry eliminates the register address overhead on the serial interface. All serial interface bits are resynchronized internally at the reference oscillator frequency. The content of the Modulation Data Register is passed to the modulation unit at the next falling edge of the divided main VCO frequency  $(F_{pd\_maid})$ .

Short  $\overline{\text{CS}}$  Through Mod\_in Pin (No Address Bits Required). A shortened serial interface write occurs when the  $\overline{\text{CS}}$  signal is from 2 to 12 clock cycles wide. The corresponding modulation data (2 to 12 bits) is simultaneously presented on the Mod\_in pin, an alternate pin used to enter modulation data directly into the Modulation Data Register with shortened  $\overline{\text{CS}}$  strobes. This mode is selected through the Modulation Control Register.

This method of data entry also eliminates the register address overhead on the serial interface and allows a different device than the one controlling the channel selection to enter the modulation data (e.g., a microcontroller for channel selection and a digital signal processor for modulation data).

All serial interface bits are internally re-synchronized at the reference oscillator frequency and the content of the Modulation Data Register is passed to the modulation unit at the next falling edge of the divided main VCO frequency ( $F_{pd\ main}$ ).

Modulation data samples in the Modulation Data Register can be from 2 to 12 bits long, and enable the user to select how many distinct frequency steps are to be used for the desired modulation scheme.

The user can also control the frequency deviation through the modulation data magnitude offset in the Modulation Control Register. This allows shifting of the modulation data to accomplish a 2<sup>m</sup> multiplication of frequency deviation.

**NOTE:** The programmable range of -0.5 to +0.5 of the main  $\Delta\Sigma$  modulator can be exceeded up to the condition where the sum of the dividend and the modulation data conform to:

$$-0.5625 \le (N_{mod} + dividend) \le +0.5625$$

When the sum of the dividend and modulation data lie outside this range, the value of  $N_{integer}$  must be changed.

For a more detailed description of direct digital modulation functionality, refer to the Skyworks Application Note, *Direct Digital*

Modulation Using the SKY72300, SKY72301, and SKY72302 Dual Synthesizers/PLLs (document number 101349).

### **Register Descriptions**

Table 1 lists the eight 16-bit registers that are used to program the SKY72310-362LF. All register writes are programmed address first, followed directly with data. MSBs are entered first. On power up, all registers are reset to 0x000 except the Divider Register at address 0x0, which is set to 0x006.

#### **Synthesizer Registers**

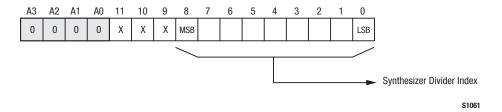

The Divider Register contains the integer portion closest to the desired fractional-N (or the integer-N) value minus 32. This register, in conjunction with the Dividend Registers (which control the fraction offset from -0.5 to +0.5), allows selection of a precise frequency. As shown in Figure 5, the value to be loaded is:

Synthesizer Divider Index = Nine-bit value for the integer portion of the synthesizer divider. Valid values for this register are from 6 to 505 (fractional-N) or 0 to 511 (integer-N).

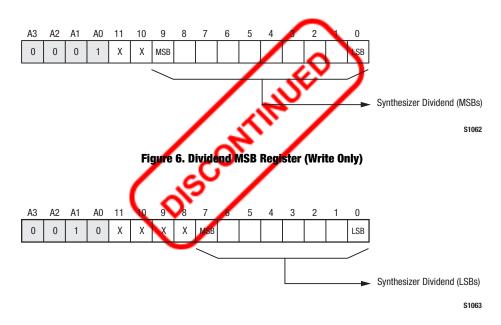

The Dividend MSB and LSB Registers control the fraction part of the desired fractional-N value and allow an offset of -0.5 to +0.5 to the main integer selected through the Divider Register. As shown in Figures 6 and 7, values to be loaded are:

- Synthesizer Dividend (MSBs) = Ten-bit value for the MSBs of the 18-bit dividend for the synthesizer.

- Synthesizer Dividend (LSBs) = Eight-bit value for the LSBs of the 18-bit dividend for the synthesizer.

The Dividend Register MSB and LSB values are 2's complement format.

**NOTE**: When in 10-bit mode, the Dividend LSB Register is not required.

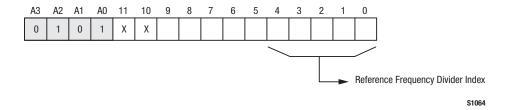

The reference frequency divider provides the reference frequency to the phase detector by dividing the crystal oscillator frequency. Divide ratios from 1 to 32 are possible for the reference frequency divider (see Table 2).

The Reference Frequency Dividers Register configures the reference frequency divider for the synthesizer. As shown in Figure 8, the values to be loaded are:

Reference Frequency Divider Index = Desired oscillator frequency division ratio -1. Default value on power up is 0, signifying that the reference frequency is not divided for the phase detector.

Table 1. SKY72310-362LF Register Map

| Address (Hex) | Register <sup>1</sup>                                 | Length (Bits)              | Address (Bits) |

|---------------|-------------------------------------------------------|----------------------------|----------------|

| 0             | Divider Register                                      | 12                         | 4              |

| 1             | Dividend MSB Register                                 | 12                         | 4              |

| 2             | Dividend LSB Register                                 | 12                         | 4              |

| 3             | Unused                                                |                            |                |

| 4             | Unused                                                |                            |                |

| 5             | Reference Frequency Dividers Register                 | 12                         | 4              |

| 6             | Phase Detector/Charge Pump Control Register           | 12                         | 4              |

| 7             | Power Down/Multiplexer Output Select Control Register | 12                         | 4              |

| 8             | Modulation Control Register                           | 12                         | 4              |

| 9             | Modulation Data Register                              | 12                         | 4              |

| _             | Modulation Data Register <sup>2</sup> — direct input  | $2 \le length \le 12 bits$ | 0              |

All registers are write only.

<sup>&</sup>lt;sup>2</sup> No address bits are required for modulation data. Any serial data between 2 and 12 bits long is considered modulation data.

Figure 5. Divider Register (Write Only)

Figure 7. Dividend LSB Register (Write Only)

**Table 2. Programming the Reference Frequency Divider**

| Decimal | Bit 4 (MSB) | Bit 3 | Bit 2 | Bit 1 | Bit 0 (LSB) | Reference Divider<br>Ratio |

|---------|-------------|-------|-------|-------|-------------|----------------------------|

| 0       | 0           | 0     | 0     | 0     | 0           | 1                          |

| 1       | 0           | 0     | 0     | 0     | 1           | 2                          |

| 2       | 0           | 0     | 0     | 1     | 0           | 3                          |

|         |             |       |       |       |             |                            |

|         |             |       |       |       |             |                            |

|         |             |       |       |       |             |                            |

| 31      | 1           | 1     | 1     | 1     | 1           | 32                         |

Figure 8. Reference Frequency Dividers Register (Write Only)

Figure 10. Power Down/Multiplexer Output Select Control Register (Write Only)

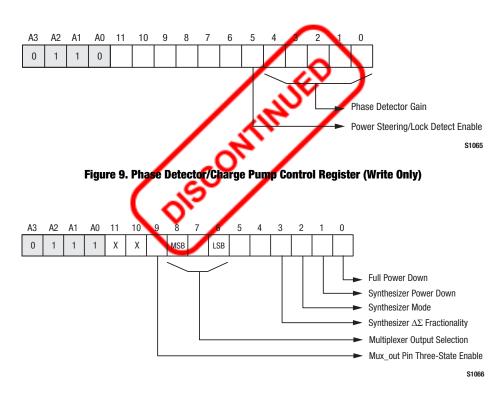

The Phase Detector/Charge Pump Control Register allows control of the gain for the phase detector and configuration of the LD/PSmain signal (pin 4) for frequency power steering or lock detection. As shown in Figure 9, the values to be loaded are:

- Phase Detector Gain = Five-bit value for programmable phase detector gain. Range is from 0 to 31 decimal for 31.25 to 1000  $\mu$ A/  $2\pi$  radian, respectively.

- Power Steering Enable = One-bit flag to enable the frequency power steering circuitry of the phase detector. When this bit is cleared, the LD/PSmain pin is configured to be a lock detect, active low, open collector pin. When this bit is set, the LD/PSmain pin is configured to be a frequency power steering pin and can be used to bypass the external loop filter to provide faster frequency acquisition.

The Power Down/Multiplexer Output Select Control Register allows control of the power-down modes, internal multiplexer output, and  $\Delta\Sigma$  synthesizer fractionality. As shown in Figure 10, the values to be loaded are:

- Full Power Down = One-bit flag to power down the SKY72310-362LF except for the reference oscillator and the serial interface. When this bit is cleared, the SKY72310-362LF is powered up. When this bit is set, the SKY72310-362LF is in full power-down mode excluding the Mux\_out signal (pin 24).

- Synthesizer Power Down = One-bit flag to power down the synthesizer. When this bit is cleared, the synthesizer is powered up. When this bit is set, the synthesizer is in power-down mode.

|  | Table | 3. | Multi | plexer | Output |

|--|-------|----|-------|--------|--------|

|--|-------|----|-------|--------|--------|

| Multiplexer Output Select<br>(Bit 8) | Multiplexer Output Select<br>(Bit 7) | Multiplexer Output Select<br>(Bit 6) | Multiplexer Output<br>(Mux_out, Pin 24)          |  |

|--------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------------------|--|

| 0                                    | 0                                    | 0                                    | Reference Oscillator                             |  |

| 0                                    | 0                                    | 1                                    | Unused                                           |  |

| 0                                    | 1                                    | 0                                    | Reference Frequency (F <sub>ref_main</sub> )     |  |

| 0                                    | 1                                    | 1                                    | Unused                                           |  |

| 1                                    | 0                                    | 0                                    | Phase Detector Frequency (F <sub>pd_main</sub> ) |  |

| 1                                    | 0                                    | 1                                    | Serial data out                                  |  |

| 1                                    | 1                                    | 0                                    | Serial interface test output                     |  |

| 1                                    | 1                                    |                                      | Unused                                           |  |

Figure 11. Modulation Control Register (Write Only)

- Synthesizer Mode = One-bit flag to power down the  $\Delta\Sigma$  modulator and fractional unit. When this bit is cleared, the synthesizer is in fractional-N mode. When this bit is set, the synthesizer is in integer-N mode.

- Synthesizer  $\Delta\Sigma$  Fractionality = One-bit flag to configure the size of the  $\Delta\Sigma$  modulator. This has a direct effect on power consumption, and on the level of fractionality and step size. When this bit is cleared, the  $\Delta\Sigma$  modulator is 18-bit with a fractionality of  $2^{18}$  and a step size of  $F_{ret\_main}/262144$ . When this bit is set, the  $\Delta\Sigma$  modulator is 10-bit with a fractionality of  $2^{10}$  and a step size of  $F_{ret\_main}/1024$ .

**NOTE**: There are no special power-up sequences required for the SKY72310-362LF.

- Multiplexer Output Selection = Three-bit value that selects which internal signal is output to the Mux\_out pin. The following internal signals are available on this pin:

- Reference oscillator: F<sub>ref</sub>

- Divided reference (post-reference frequency divider): F<sub>ref\_main</sub>

- Phase detector frequency (post-frequency divider): F<sub>pd\_main</sub>

- Serial data out for loop-back and test purposes

Refer to Table 3 for more information.

Mux\_out Pin Tri-State Enable = One-bit flag to tri-state the Mux\_out pin. When this bit is cleared, the Mux\_out pin is enabled. When this bit is set. the Mux\_out pin is tri-stated.

The Modulation Control Register is used to configure the modulation unit of the main synthesizer. The modulation unit adds or subtracts a frequency offset to the selected center frequency at which the main synthesizer operates. The size of the modulation data sample, controlled by the duration of the  $\overline{\text{CS}}$  signal, can be from 2 to 12 bits wide to provide from 4 to 4096 selectable frequency offset steps.

The modulation data magnitude offset selects the magnitude multiplier for the modulation data and can be from 0 to 8. As shown in Figure 11, the values to be loaded are:

- Modulation Data Magnitude Offset = Four-bit value that indicates the magnitude multiplier (m) for the modulation data samples. Valid values range from 0 to 13, effectively providing a 2<sup>m</sup> multiplication of the modulation data sample.

Data pin. When this bit is set, modulation data samples are to be presented on the Mod in pin.

Modulation Address Disable = One-bit flag to indicate the

presence of the address as modulation data samples are

presented on either the Mod\_in or Data pins. When this bit is

cleared, the address is presented with the modulation data

samples (i.e., all transfers are 16 bits long). When this bit is set,

no address is presented with the modulation data samples (i.e.,

all transfers are 2 to 12 bits long).

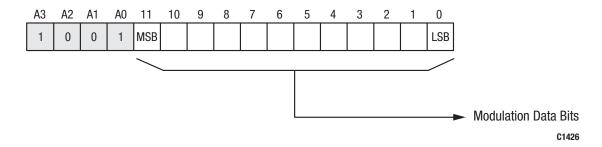

The Modulation Data Register is used to load the modulation data samples to the modulation unit. These values are transferred to the modulation unit on the falling edge of  $F_{pd\_main}$  where they are passed to the main  $\Delta\Sigma$  modulator at the selected magnitude offset on the next falling edge of  $F_{pd\_main}$ . Modulation Data Register values are 2's complement format. As shown in Figure 12, the value to be loaded is:

Modulation Data Bits = Modulation data samples that represent the instantaneous frequency offset to the selected main synthesizer frequency (selected channel) before being affected by the modulation data magnitude offset.

# **Package and Handling Information**

Since the device package is sensitive to moisture absorption, it is baked and vacuum packed before shipping. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

The SKY72310-362LF is rated to Moisture Sensitivity Level 3 (MSL3) at 260 °C. It can be used for lead or lead-free soldering.

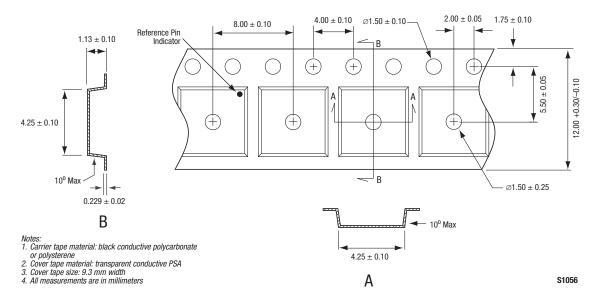

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format. For packaging details, refer to the Skyworks Application Note, *Tape and Reel*, document number 101568.

# **Electrical and Mechanical Specifications**

Signal pin assignments and functional pin descriptions are described in Table 4. The absolute maximum ratings of the SKY72310-362LF are provided in Table 5. The recommended operating conditions are specified in Table 6 and electrical specifications are provided in Table 7.

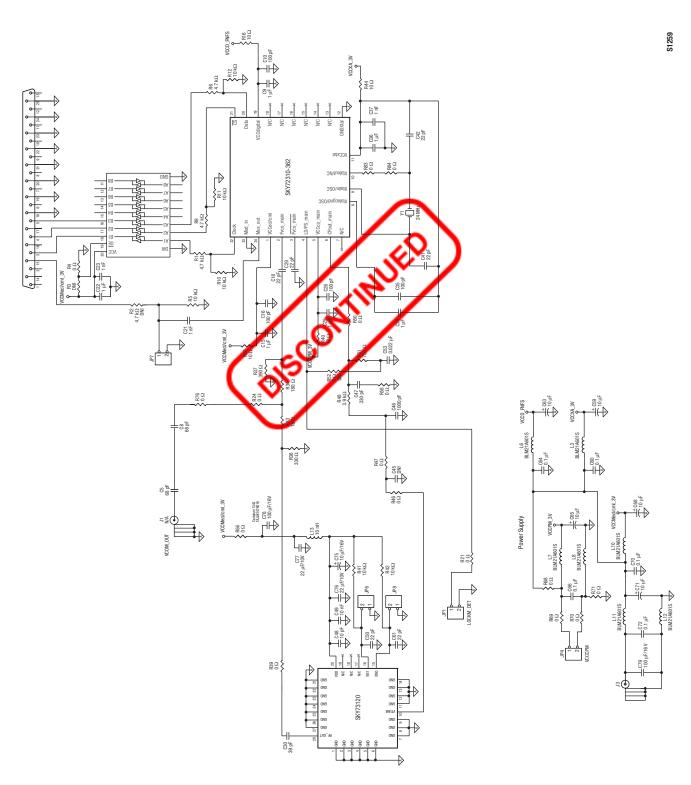

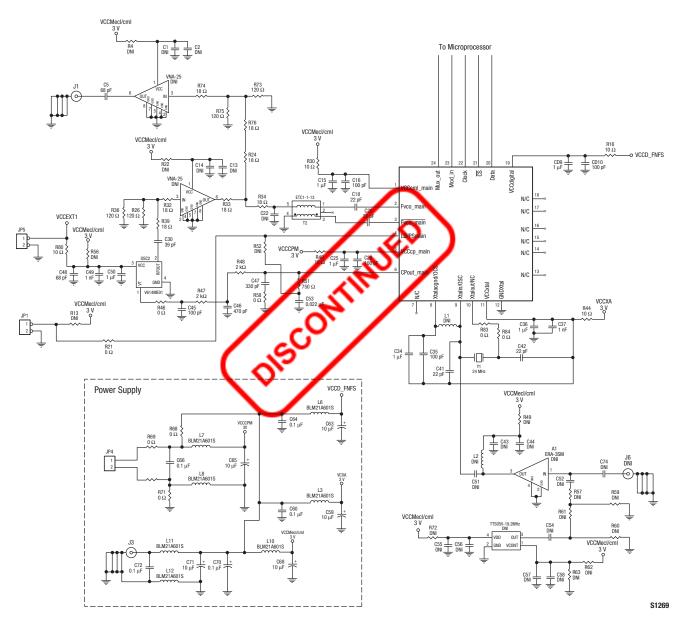

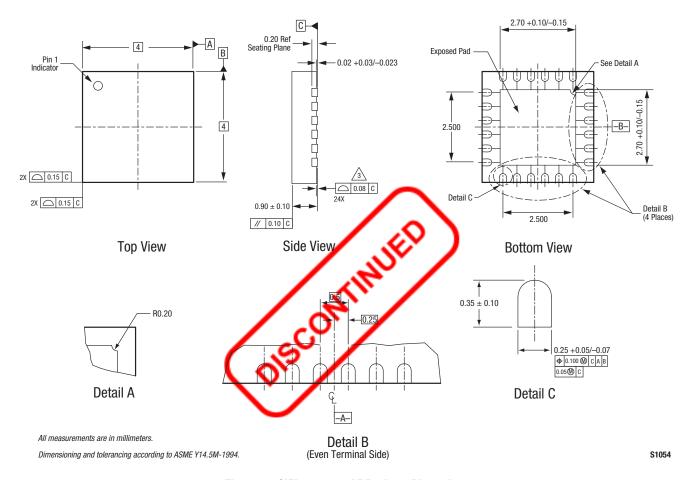

Figure 13 provides a schematic diagram for the SKY72310-362LF using Skyworks SKY73120 890-960 MHz VCO. Figure 14 provides a schematic diagram for the SKY72310-362LF using a non-Skyworks VCO. Figure 15 shows the package dimensions, and Figure 16 provides the tape and reel dimensions.

# **Electrostatic Discharge (ESD) Sensitivity**

The SKY72310-362LF is a static-sensitive electronic device. Do not operate or store near strong electrostatic fields. Take proper ESD precautions.

Figure 12. Modulation Data Register (Write Only)

**Table 4. SKY72310-362LF Signal Descriptions**

| Pin | Pin Name                | Туре             | Description                                                                                                                                                                                                                                                                |

|-----|-------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | VCCecl/cml              | Power and ground | ECL/CML, 3 V. Removing power safely powers down the associated divider chain and charge pump.                                                                                                                                                                              |

| 2   | Fvco_main               | Input            | Main VCO differential input.                                                                                                                                                                                                                                               |

| 3   | Fvco_main               | Input            | Main VCO complimentary differential input.                                                                                                                                                                                                                                 |

| 4   | LD/PS_main              | Analog output    | Programmable output pin. Indicates phase detector out-of-lock as an active low pulsing open collector output (high impedance when lock is detected), or helps the loop filter steer the VCO. This pin is configured using the Phase Detector/Charge Pump Control Register. |

| 5   | VCCcp_main <sup>1</sup> | Power and ground | Charge pump supply, 3 to 5 V. Removing power safely powers down the associated divider chain and charge pump.                                                                                                                                                              |

| 6   | CPout_main              | Analog output    | Charge pump output. The gain of the charge pump phase detector is controlled by the Phase Detector/Charge Pump Control Register.                                                                                                                                           |

| 7   | N/C                     | -                | No connection                                                                                                                                                                                                                                                              |

| 8   | Xtalacgnd/OSC           | Ground/input     | Reference crystal AC ground or external oscillator differential input.                                                                                                                                                                                                     |

| 9   | Xtalin/OSC              | Input            | Reference crystal input or external oscillator differential input.                                                                                                                                                                                                         |

| 10  | Xtalout/NC              | Input            | Reference crystal output or no connect.                                                                                                                                                                                                                                    |

| 11  | VCCxtal                 | Power and ground | Crystal oscillator ECL/CML, 3 V.                                                                                                                                                                                                                                           |

| 12  | GNDxtal                 | Power and ground | Crystal oscillator ground.                                                                                                                                                                                                                                                 |

| 13  | N/C                     | -                | No connection                                                                                                                                                                                                                                                              |

| 14  | N/C                     | - (              | No connection                                                                                                                                                                                                                                                              |

| 15  | N/C                     | - (              | No connection                                                                                                                                                                                                                                                              |

| 16  | N/C                     | -                | No connection                                                                                                                                                                                                                                                              |

| 17  | N/C                     | -                | No connection                                                                                                                                                                                                                                                              |

| 18  | N/C                     | -                | No connection                                                                                                                                                                                                                                                              |

| 19  | VCCdigital <sup>1</sup> | Power and ground | Digital supply, 3 V.                                                                                                                                                                                                                                                       |

| 20  | Data                    | Digital input    | Serial address and data input pin. Address bits are followed by data bits.                                                                                                                                                                                                 |

| 21  | <del>CS</del>           | Digital input    | Active low enable pin. Enables loading of address and data on the Data pin on the rising edge of Clock. When $\overline{\text{CS}}$ goes high, data is transferred to the register indicated by the address. Subsequent clock edges are ignored.                           |

| 22  | Clock                   | Digital input    | Clock signal pin. When $\overline{\text{CS}}$ is low, the register address and data are shifted in address bits first on the Data pin on the rising edge of Clock.                                                                                                         |

| 23  | Mod_in                  | Digital input    | Alternate serial modulation data input pin. Address bits are followed by data bits.                                                                                                                                                                                        |

| 24  | Mux_out                 | Digital output   | Internal multiplexer output. Selects from oscillator frequency, reference frequency, divided VCO frequency, serial data out, or testability signals. This pin can be tri-stated from the synthesizer registers.                                                            |

$<sup>^{1}\,</sup>$  Associated pairs of power and ground pins must be decoupled using 0.1  $\mu\text{F}$  capacitors.

#### **Table 5. Absolute Maximum Ratings<sup>1</sup>**

| Parameter                          | Min | Max  | Units |  |  |  |

|------------------------------------|-----|------|-------|--|--|--|

| Maximum analog RF supply voltage   |     | 3.6  | VDC   |  |  |  |

| Maximum digital supply voltage     |     | 3.6  | VDC   |  |  |  |

| Maximum charge pump supply voltage |     | 5.25 | VDC   |  |  |  |

| Storage temperature                | -65 | +150 | °C    |  |  |  |

| Operating temperature              | -40 | +85  | °C    |  |  |  |

Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal values.

#### DATA SHEET • SKY72310-362LF: FREQUENCY SYNTHESIZER

**Table 6. Recommended Operating Conditions**

| Parameter                  | Min | Max | Units |

|----------------------------|-----|-----|-------|

| Analog RF supplies         | 2.7 | 3.3 | VDC   |

| Digital supply             | 2.7 | 3.3 | VDC   |

| Charge pump supplies       | 2.7 | 5.0 | VDC   |

| Operating temperature (TA) | -40 | +85 | °C    |

# **Table 7. Electrical Characteristics (1 of 2)**

(VDD = 3 V, TA = 25 °C, Unless Otherwise Noted)

| Parameter                                  | Symbol               | Test Conditions                                                                                                    | Min                                                    | Тур                     | Max                     | Units              |

|--------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|-------------------------|-------------------------|--------------------|

| Power Consumption                          |                      |                                                                                                                    |                                                        |                         |                         |                    |

| Total power consumption                    | PTOTAL               | Charge pump current of 200 µA, synthesizer fractional, FREG_MAIN = 20 MHz                                          |                                                        | 37.5                    |                         | mW                 |

| Power-down current                         | Icc-pwdn             | 4                                                                                                                  |                                                        | 10 (Note 1)             |                         | μА                 |

| Reference Oscillator                       |                      |                                                                                                                    |                                                        |                         |                         |                    |

| Reference oscillator frequency             | Fosc                 | ~ /                                                                                                                |                                                        |                         | 50                      | MHz                |

| Oscillator sensitivity (as a buffer)       | Voso                 | AC coupled, single-ended                                                                                           | 0.1                                                    |                         | 2.0                     | Vpp                |

| Frequency shift versus supply voltage      | FSHIFT_SUPPLY        | 2.7 V ≤ VXTAL ≤ 3.3 V                                                                                              |                                                        |                         | ±0.3                    | ppm                |

| VCO                                        |                      |                                                                                                                    |                                                        |                         |                         |                    |

| Synthesizer operating frequency            | Fvco_main            | Sinusoidal, -40 °C to +85 °C                                                                                       | 100 (Note 2)                                           |                         | 2100                    | MHz                |

| RF input sensitivity                       | Vvco                 | AC coupled                                                                                                         | 50                                                     |                         | 250                     | $mV_{\text{peak}}$ |

| RF input impedance                         | Zvco_in              |                                                                                                                    |                                                        | 94 - j140<br>@ 1200 MHz |                         | Ω                  |

| Fractional-N tuning step size              | $\Delta F$ STEP_MAIN |                                                                                                                    | Fref_main/2 <sup>18</sup> or Fref_main/2 <sup>10</sup> |                         |                         | Hz                 |

| Phase Noise                                |                      |                                                                                                                    |                                                        |                         |                         |                    |

| Phase noise floor                          | P <sub>nf</sub>      | Measured inside the loop<br>bandwidth using 25 MHz<br>reference frequency,<br>-40 °C to +85 °C                     |                                                        | -128<br>+ 20 Log (N)    |                         | dBc/Hz             |

| Phase Detector and Charge Pump             |                      |                                                                                                                    |                                                        |                         |                         |                    |

| Phase detector frequency                   | Fref_main            | -40 °C to +85 °C                                                                                                   |                                                        |                         | 25                      | MHz                |

| Charge pump output source current          | ICP-SOURCE           | Vcp = 0.5 VCCcp                                                                                                    | 125                                                    |                         | 1000                    | μΑ                 |

| Charge pump output sink current            | ICP-SINK             | Vcp = 0.5 VCCcp                                                                                                    | -125                                                   |                         | -1000                   | μΑ                 |

| Charge pump accuracy                       | ICP-ACCURACY         |                                                                                                                    |                                                        | ±20                     |                         | %                  |

| Charge pump output voltage linearity range | ICP VS VCP           | $\begin{array}{l} 0.5~\textrm{V} \leq \textrm{Vcp} \leq (\textrm{VCCcp} \\ \textrm{-}~0.5~\textrm{V}) \end{array}$ | GND + 400                                              |                         | VCC <sub>CP</sub> - 400 | mV                 |

| Charge pump current versus temperature     | ICP VS T             | $V_{CP} = 0.5 \text{ VCC}_{CP}$<br>-40 °C < T < +85 °C                                                             |                                                        |                         | 5                       | %                  |

| Charge pump current versus voltage         | ICP VS VCP           | 0.5 V ≤ V <sub>CP</sub> ≤ (VCC <sub>CP</sub> - 0.5 V)                                                              |                                                        |                         | 8                       | %                  |

<sup>1</sup> A 5 V charge pump power supply on pin 5 results in higher power-down leakage current.

The minimum synthesizer frequency is 12 x Fosc, where Fosc is the frequency at the Xtalin/OSC pin.

# Table 7. Electrical Characteristics (2 of 2) (VDD = 3 V. TA = 25 °C. Unless Otherwise Noted)

Figure 13. SKY72310-362LF Application Schematic (With SKY73120 VCO)

Figure 14. SKY72310-362LF Application Schematic (With Non-Skyworks VCO)

Figure 15. SKY72310-362LF Package Dimensions

Figure 16. SKY72310-362LF Tape and Reel Dimensions

# **Ordering Information**

| Part Number    | Product Description                                          | Evaluation Board Part Number |

|----------------|--------------------------------------------------------------|------------------------------|

| SKY72310-362LF | Spur-Free, 2.1 GHz Single Fractional-N Frequency Synthesizer | SKY72310-EVB                 |

Copyright © 2007-2008, 2017-2018 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks and the Skyworks symbol are trademarks or registered trademarks of Skyworks Solutions, Inc. or its subsidiaries in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at www.skyworksinc.com, are incorporated by reference.